Pourquoi en 64bit l'adresse virtuelle est courte de 4 bits (48bit de long) par rapport à l'adresse physique (52 bit de long)?

Dans le livre "Programmation de Bas Niveau: C, le Montage et l'Exécution du Programme sur l'Architecture Intel® 64" j'ai lu:

chaque adresse virtuelle 64 bits (par exemple, celles que nous utilisons dans nos programmes)) se compose de plusieurs champs. L'adresse elle-même est en fait seulement 48 bits large; il est étendu à une adresse canonique 64 bits. Son caractéristique est que ses 17 bits gauches sont égaux. Si la condition est pas satisfait, l'adresse est immédiatement rejeté lorsqu'il est utilisé. Puis 48 bits d'adresse virtuelle sont transformés en 52 bits de physique adresse avec l'aide de tables spéciales.

pourquoi la différence en 4 bits entre l'adresse virtuelle et l'adresse physique?

1 réponses

je crois que vous parlez de x86-64, ma réponse est basée sur cette architecture.

Lorsqu'il est utilisé en mode 64 bits, le CPU utilise une nouvelle fonctionnalité pour traduire les adresses virtuelles en adresses physiques connues sous le nom de PAE-Physical address extension .

Inventé à l'origine pour briser la limite de 4GiB tout en utilisant encore des pointeurs 32 bits, cette fonctionnalité implique l'utilisation de 4 niveaux de tables.

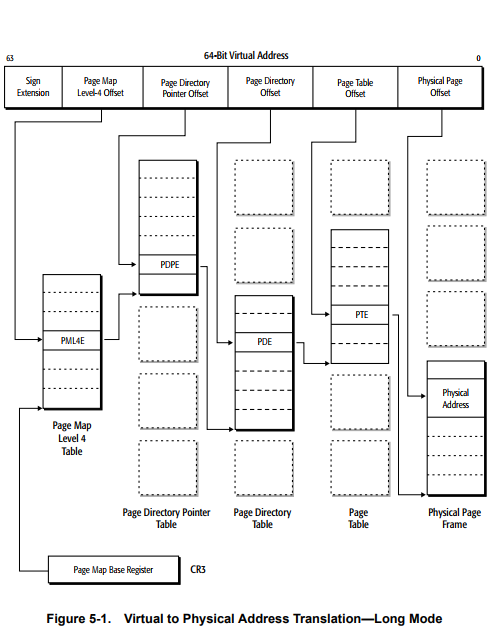

Chaque table donne un pointeur vers la table suivante, jusqu'à l'extrémité droite qui donne les bits supérieurs de l'adresse physique. Pour obtenir une idée regardez cette image de la AMD64 Manuel de programmation D'Architecture :

la raison d'être de tous ces tableaux est sparsity : les métadonnées pour traduire les adresses virtuelles en les adresses physiques sont énormes - si nous n'utilisions que des pages de 4KiB, nous aurions besoin 2 64 - 12 = 2 52 entrées pour couvrir l'ensemble de l'espace d'adresse 64 bits.

Les Tables permettent une approche clairsemée, seules les entrées nécessaires sont peuplées en mémoire.

cette conception se reflète dans la façon dont l'adresse virtuelle est divisée (et donc, indirectement, dans le nombre de niveaux), seuls les passages de 9 bits sont utilisés pour indexer les tableaux à chaque niveau.

À partir du bit 12 inclus, cela donne: niveau 1 -> 12-20, niveau 2 -> 21-29, niveau 3 -> 30-38, niveau 4 -> 39-47.

cela explique la limite actuelle d'implémentation de seulement 48 bits d'espace d'adresse virtuel.

Notez qu'au niveau de l'instruction, lorsque des adresses logiques sont utilisées, nous avons un support complet pour les adresses 64 bits.

Un soutien complet est également disponible au niveau de la segmentation, la partie qui traduit les adresses logiques en adresses linéaires.

Donc la limitation vient de PAE.

Mon personnelle avis est que AMD se sont précipités pour être le premier à embarquer un PROCESSEUR x86 avec prise en charge 64 bits et réutilisés PAE, il correctifs à un nouveau niveau d'indirection à traduire jusqu'à 48 bits.

Notez que Intel et AMD permettent à une future implémentation d'utiliser 64 bits pour l'adresse virtuelle (probablement avec plus de tables).

cependant, les deux sociétés ont fixé une limite stricte de 52 bits pour l'adresse physique. Pourquoi?

la réponse se trouve encore dans la façon dont le travail de paging.

En mode 32 bits, chaque entrée dans chaque table est de 32 bits de large; les bits bas sont utilisés comme drapeaux (puisque les exigences d'alignement les rendent inutiles pour le processus de traduction) mais les bits supérieurs ont tous été utilisés pour la traduction, donnant un 32/32 virtuel / physique traduction.

Il est important de souligner que tous les 32 bits ont été utilisés, alors que certains des bits inférieurs n'ont pas été utilisés comme drapeaux, Intel les a marqués comme "ignorés" ou "disponibles" ce qui signifie que le système D'exploitation était libre de les utiliser.

quand Intel a introduit PAE, ils avaient besoin de 4 bits supplémentaires (PAE était de 36 bits à l'époque) et la chose logique à faire était de double la taille de chaque entrée car cela crée une mise en page plus efficace qu'une entrée de 40 bits.

Cela a donné à Intel beaucoup d'espace disponible et ils l'ont marqué comme réservé (cela peut être mieux observé dans les versions plus anciennes des manuels de SDM Intel, comme celui-ci ).

avec le temps, de nouveaux attributs étaient nécessaires dans une entrée, le plus célèbre étant le XD/NX bit .

Les touches de Protection sont également une caractéristique relativement nouvelle qui prend de la place dans un entrée.

Cela montre qu'une traduction virtuelle/physique 64/64 bits n'est plus possible avec L'ISA actuelle.

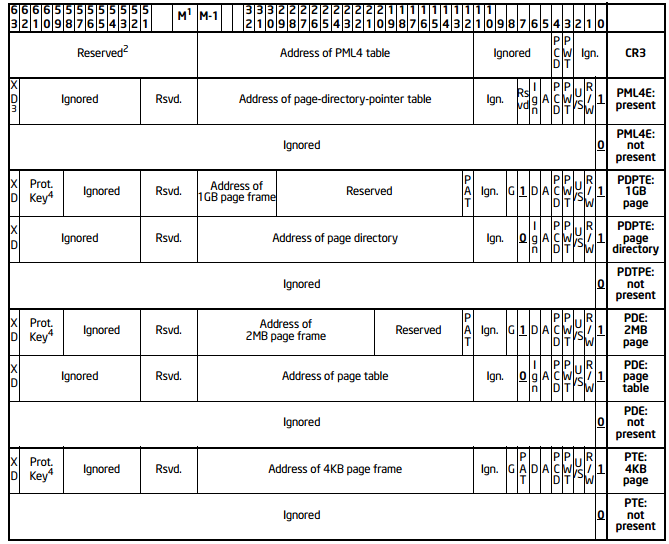

pour une référence visuelle, voici le format des entrées du tableau PAE 64 bits:

il montre qu'une adresse physique 64 bits n'est pas possible (pour les pages énormes Il ya encore un moyen de corriger cela, mais compte tenu de la disposition des bits qui semble peu probable) mais ça n'explique pas pourquoi AMD a fixé la limite à 52 bits.

c'est difficile à dire.

Certainement, la taille de l'espace d'adresse physique a quelque matériel coût associé à elle: plus de pins (bien qu'avec le contrôleur de mémoire intégré, cela est atténué que les spécifications de DDR multiplexent beaucoup de signaux) et plus d'espace dans les caches/TLBs.

Dans cette question (similaire mais pas assez faites-en un duplicata) une réponse villes Wikipedia, qui à son tour cite prétendument AMD, affirmant que les ingénieurs D'AMD ont fixé la limite à 52 bits après avoir dûment pris en considération les avantages et les coûts.

je partage ce que Hans Passant a écrit il y a plus de 6 ans : les mécanismes de pagination actuels ne sont pas adaptés à une adresse physique 64 bits et c'est probablement la raison pour laquelle Intel et AMD ne se sont jamais souciés de garder les bits élevés dans chaque entrée réservée.

les deux entreprises savent que la technologie approchant la limite de 52 bits, elle sera également très différente de sa forme réelle.

Par le temps, ils ont conçu un meilleur mécanisme de la mémoire en général, de sorte qu'ils évitées sur-l'ingénierie de l'existant.